- RS Stock No.:

- 249-4404

- Mfr. Part No.:

- 9DBV0431AKILF

- Manufacturer:

- Renesas Electronics

Temporarily out of stock - back order for despatch 14/01/2025, delivery within 6 working days

Added

Price (VAT excluded) Each (In a Tray of 490)

TWD83.50

(exc. GST)

TWD87.68

(inc. GST)

| Units | Per unit | Per Tray* |

| 490 + | TWD83.50 | TWD40,915.00 |

| *price indicative | ||

- RS Stock No.:

- 249-4404

- Mfr. Part No.:

- 9DBV0431AKILF

- Manufacturer:

- Renesas Electronics

Product overview and Technical data sheets

Legislation and Compliance

Product Details

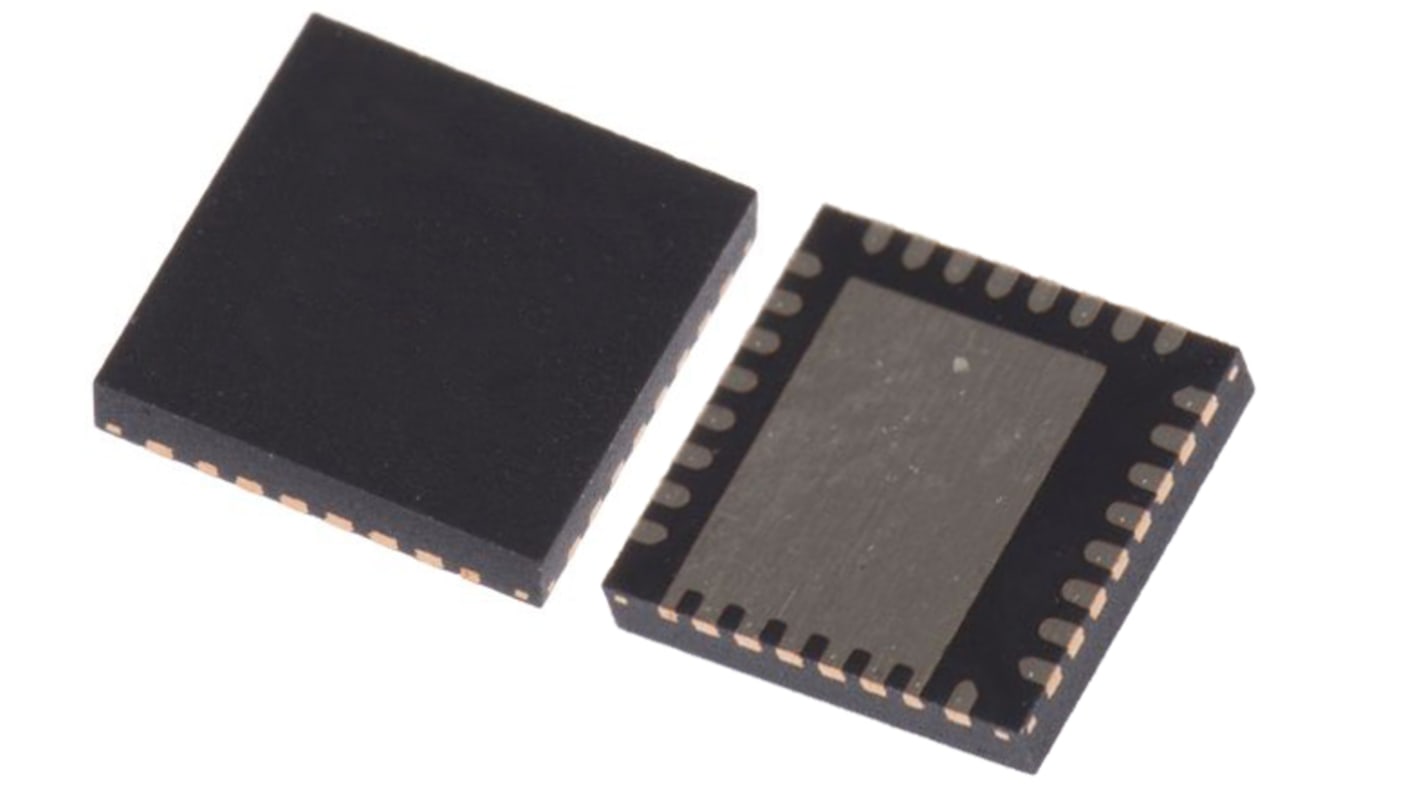

The Renesas Electronics 9DBV0431 is a 4-output very low power buffer for 100 MHz PCIe Gen1, Gen2 and Gen3 applications. It can also be used for 50M or 125M Ethernet Applications via software frequency selection. The device has 4 output enables for clock management.

1.8 V operation: minimal power consumption

OE# pins: support DIF power management

HCSL compatible differential input: can be driven by common clock sources

LP-HCSL differential clock outputs: reduced power and board space

Programmable slew rate for each output: allows tuning for various line lengths

Programmable output amplitude: allows tuning for various application environments

Pin/software selectable PLL bandwidth and PLL Bypass: minimize phase jitter for each application

Outputs blocked until PLL is locked: clean system start-up

Software selectable 50 MHz or 125 MHz PLL operation: useful for Ethernet applications

Configuration can be accomplished with strapping pins: SMBus interface not required for device control

3.3 V tolerant SMBus interface works with legacy controllers

OE# pins: support DIF power management

HCSL compatible differential input: can be driven by common clock sources

LP-HCSL differential clock outputs: reduced power and board space

Programmable slew rate for each output: allows tuning for various line lengths

Programmable output amplitude: allows tuning for various application environments

Pin/software selectable PLL bandwidth and PLL Bypass: minimize phase jitter for each application

Outputs blocked until PLL is locked: clean system start-up

Software selectable 50 MHz or 125 MHz PLL operation: useful for Ethernet applications

Configuration can be accomplished with strapping pins: SMBus interface not required for device control

3.3 V tolerant SMBus interface works with legacy controllers

For products that are Customized and under Non-cancellable & Non-returnable, Sales & Conditions apply.

Specifications

Attribute | Value |

|---|---|

| Number of Elements per Chip | 4 |

| Maximum Supply Current | 4 mA |

| Maximum Input Frequency | 137.5MHz |

| Mounting Type | Surface Mount |

| Package Type | QFN |

| Pin Count | 32 |