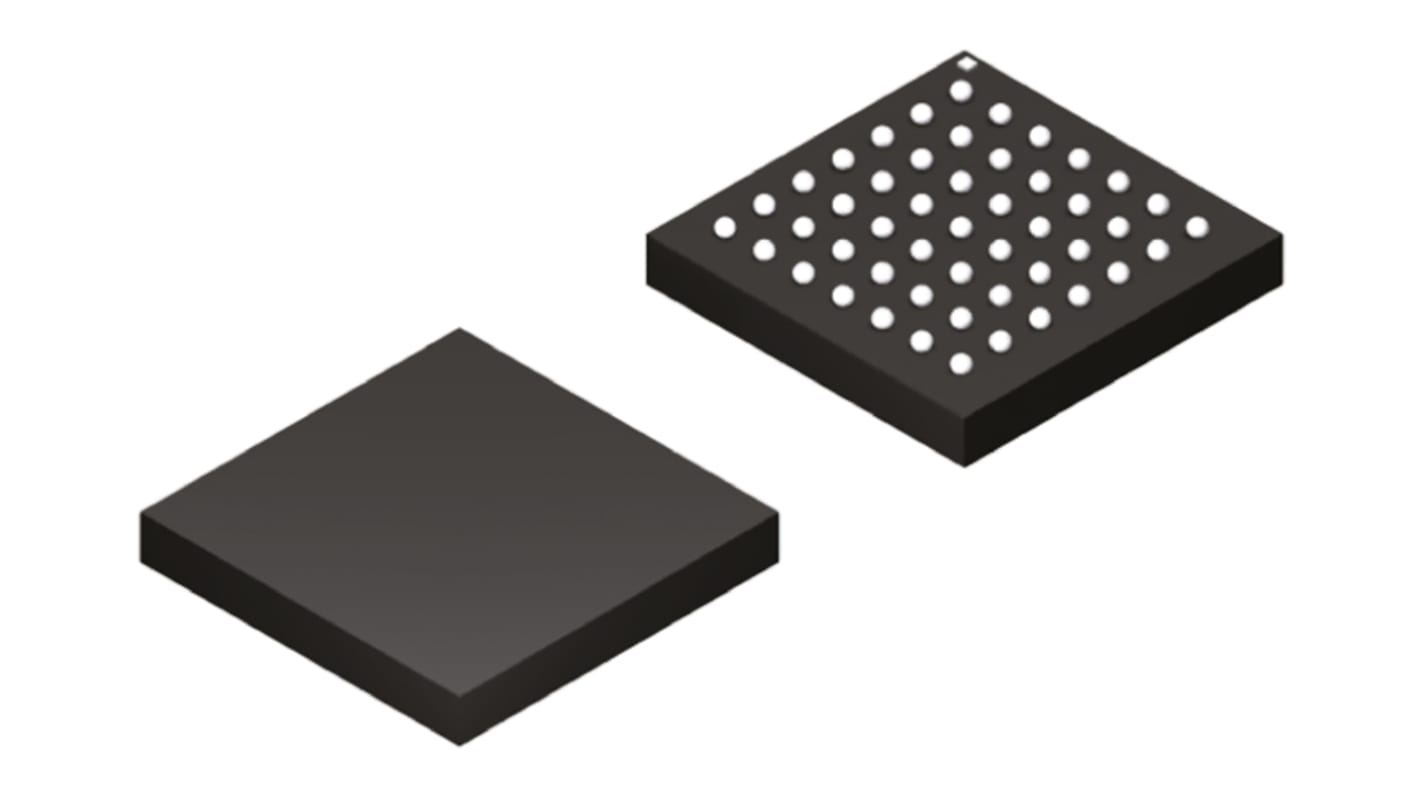

Lattice FPGA iCE40 LP/HX 1280 Cells, 64 kB 160 Blocks, 49-Pin UCBGA

- RS Stock No.:

- 168-4224

- Mfr. Part No.:

- ICE40LP1K-CM49

- Manufacturer:

- Lattice Semiconductor

The image is for reference only, please refer to product details and specifications

Currently unavailable

We don't know if this item will be back in stock, RS intend to remove it from our range soon.

- RS Stock No.:

- 168-4224

- Mfr. Part No.:

- ICE40LP1K-CM49

- Manufacturer:

- Lattice Semiconductor

Specifications

Product overview and Technical data sheets

Legislation and Compliance

Product Details

Find similar products by selecting one or more attributes.

Select all | Attribute | Value |

|---|---|---|

| Brand | Lattice Semiconductor | |

| Product Type | FPGA | |

| Series | iCE40 LP/HX | |

| Number of Logic Cells | 1280 | |

| Number of Logic Units | 160 | |

| Number of Registers | 1280 | |

| Mount Type | Surface | |

| Package Type | UCBGA | |

| Minimum Supply Voltage | 1.14V | |

| Pin Count | 49 | |

| Maximum Supply Voltage | 1.26V | |

| Minimum Operating Temperature | -40°C | |

| Number of RAM Bits | 64kB | |

| Maximum Operating Temperature | 85°C | |

| Standards/Approvals | Halogen Free | |

| Height | 0.9mm | |

| Length | 3mm | |

| Automotive Standard | No | |

| Select all | ||

|---|---|---|

Brand Lattice Semiconductor | ||

Product Type FPGA | ||

Series iCE40 LP/HX | ||

Number of Logic Cells 1280 | ||

Number of Logic Units 160 | ||

Number of Registers 1280 | ||

Mount Type Surface | ||

Package Type UCBGA | ||

Minimum Supply Voltage 1.14V | ||

Pin Count 49 | ||

Maximum Supply Voltage 1.26V | ||

Minimum Operating Temperature -40°C | ||

Number of RAM Bits 64kB | ||

Maximum Operating Temperature 85°C | ||

Standards/Approvals Halogen Free | ||

Height 0.9mm | ||

Length 3mm | ||

Automotive Standard No | ||

- COO (Country of Origin):

- KR

Field Programmable Gate Arrays, Lattice Semiconductor

An FPGA is a semiconductor device consisting of a Matrix of Configurable Logic Blocks (CLBs) connected through programmable interconnects. The user determines these interconnections by programming SRAM. A CLB can be simple (AND, OR gates, etc) or complex (a Block of RAM). The FPGA allows changes to be MADE to a design even after the device is soldered into a PCB.